One-stop Electronic Manufacturing Services, tulungan kang madaling makuha ang iyong mga produktong elektroniko mula sa PCB at PCBA

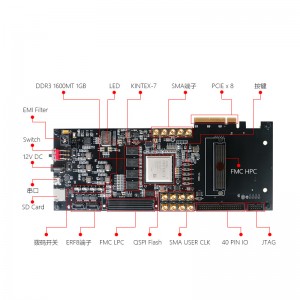

FPGA Xilinx K7 Kintex7 PCIe optical fiber na komunikasyon

- DDR3 SDRAM: 16GB DDR3 64bit bus, data rate na 1600Mbps

- QSPI Flash: Isang piraso ng 128mbit QSPIFLASH, na maaaring gamitin para sa FPGA configuration file at imbakan ng data ng user

- PCLEX8 interface: Ang karaniwang PCLEX8 interface ay ginagamit upang makipag-ugnayan sa PCIE na komunikasyon ng motherboard ng computer. Sinusuportahan nito ang pamantayan ng PCI, Express 2.0. Ang rate ng komunikasyon sa solong channel ay maaaring kasing taas ng 5Gbps

- USB UART serial port: Isang serial port, kumonekta sa PC sa pamamagitan ng miniusb cable para magsagawa ng serial communication

- Micro SD card: Microsd card seat sa lahat ng paraan, maaari mong ikonekta ang karaniwang Microsd card

- Temperature sensor: isang temperature sensor chip LM75, na maaaring subaybayan ang temperatura ng kapaligiran sa paligid ng development board

- FMC extension port: isang FMC HPC at isang FMCLPC, na maaaring tugma sa iba't ibang karaniwang expansion board card

- ERF8 high-speed connection terminal: 2 ERF8 port, na sumusuporta sa ultra-high-speed signal transmission 40pin extension: nakalaan ng pangkalahatang extension IO interface na may 2.54mm40pin, ang epektibong O ay may 17 pares, sumusuporta sa 3.3V

- Maaaring ikonekta ng peripheral na koneksyon ng level at ng 5V level ang peripheral peripheral ng iba't ibang general-purpose 1O interface

- SMA terminal; 13 mataas na kalidad na gold-plated SMA head, na maginhawa para sa mga user na makipagtulungan sa mga high-speed AD/DA FMC expansion card para sa pagkolekta at pagproseso ng signal

- Pamamahala ng Orasan: Multi-clock source. Kabilang dito ang 200MHz system differential clock source SIT9102

- Differential crystal oscillating: 50MHz crystal at SI5338P programmable clock management chip: nilagyan din ng

- 66MHz EMCLK. Maaaring tumpak na umangkop sa iba't ibang dalas ng orasan ng paggamit

- JTAG port: 10 stitches 2.54mm standard JTAG port, para sa pag-download at pag-debug ng mga FPGA program

- Sub-reset voltage monitoring chip: isang piraso ng ADM706R voltage monitoring chip, at ang button na may button ay nagbibigay ng global reset signal para sa system

- LED: 11 LED na ilaw, ipahiwatig ang power supply ng board card, config_done signal, FMC

- Signal ng power indicator, at 4 na user LED

- Susi at switch: 6 na susi at 4 na switch ay mga pindutan ng pag-reset ng FPGA,

- Ang button ng Program B at 4 na key ng user ay binubuo. 4 single-knife double throw switch

Isulat ang iyong mensahe dito at ipadala ito sa amin

Mga kategorya ng produkto

-

Telepono

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype